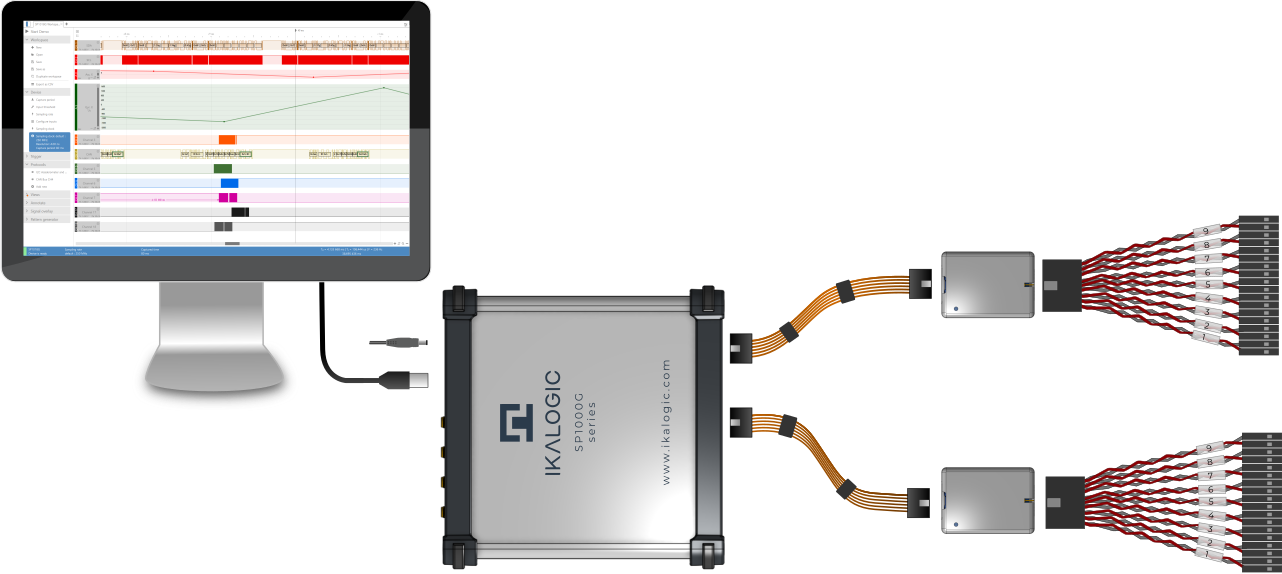

SP1000G Series

logic analyzers & pattern generators

Up to 54 channels, 1GSPS, and fully scriptable signal generation

The SP1000G series combines high-performance logic analysis and pattern generation in a single device. With up to 54 channels and a maximum sampling rate of 1GSPS, the SP1000G is built for development, validation, and semiconductor QA services. It’s the perfect tool for engineers needing to capture, decode, and inject complex signal patterns into embedded systems for DFT (Design For Test) setups.

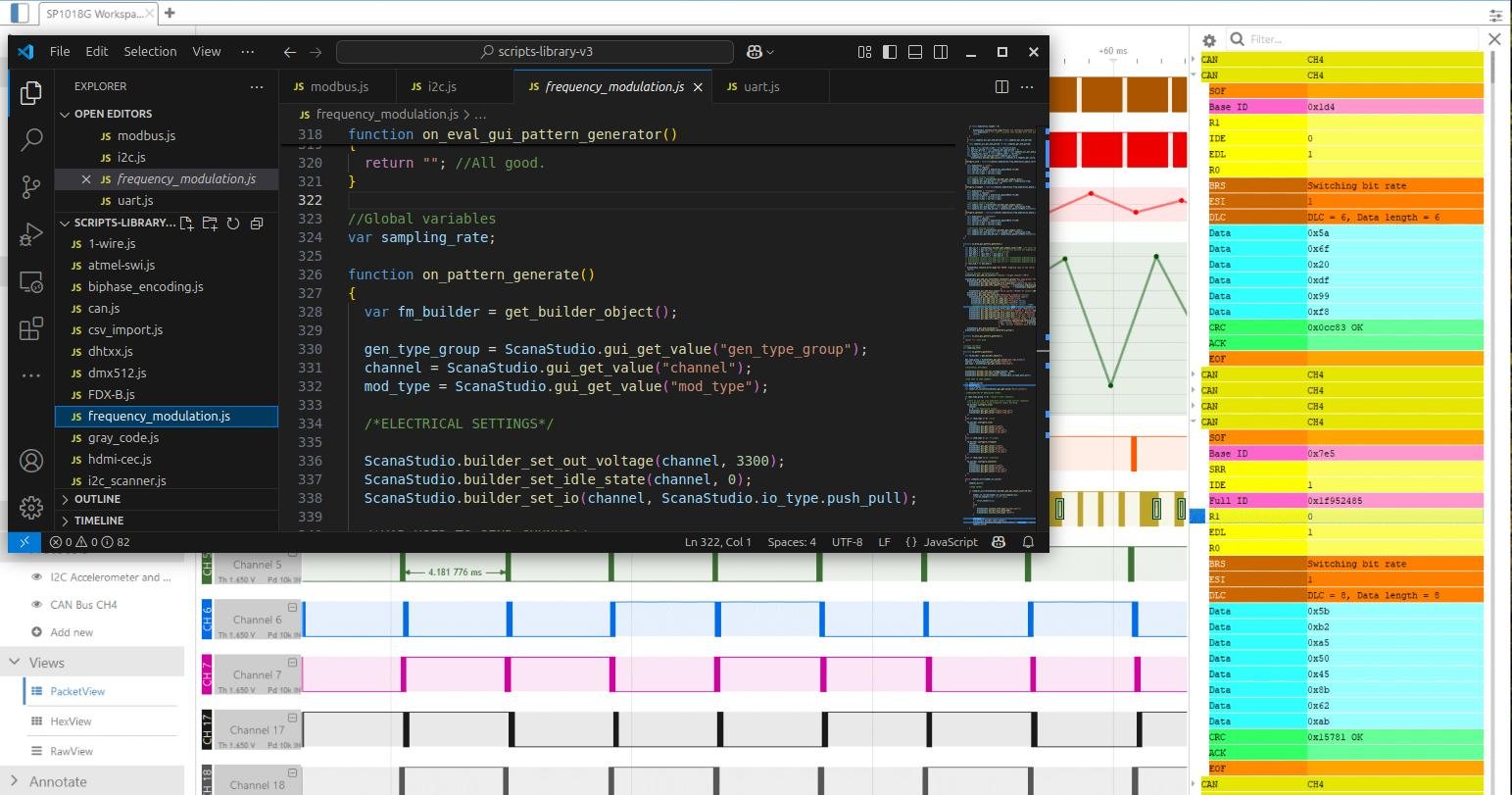

Powered by ScanaStudio, it supports interactive use and advanced scripting. Protocols such as SPI, I2C, UART, parallel, memory buses, and more are natively supported and scriptable. Explore the full list of protocols.

- Capture & Generate

- Semiconductor Test & DFT

- 1GSPS on All Channels

- Sync & Integration

- Scripting powered

Analyze complex digital signals and inject precisely-timed patterns with one powerful tool.

SP1000G devices combine logic analysis and pattern generation, each with its own dedicated memory and control engine.

The SP1000G series is built for Design-for-Test applications, where scripted signal generation and logic capture are critical.

Whether emulating test vectors or reacting to DUT behavior, every sequence can be fully customized with ScanaStudio Scripts according to your specifications.

Unlike many instruments that reduce performance with more channels, SP1000G devices maintain full-speed 1GSPS sampling—no compromise, even on the 54-channel model.

Coupled with real-time sample compression and up to 12 Gb of internal memory, the SP1000G adapts to your most demanding capture scenarios.

Synchronize multiple instruments using trigger I/O and external clock inputs.

The SP1000G series integrates seamlessly into larger setups, enabling precise coordination with other test equipment. Whether you’re triggering acquisitions from an external event, clocking in sync with a DUT, or chaining multiple SP1000G units together, everything stays perfectly timed—down to the nanosecond. Timestamp alignment across multiple units ensures consistent data correlation, making SP1000G ideal for distributed or multi-point signal analysis.

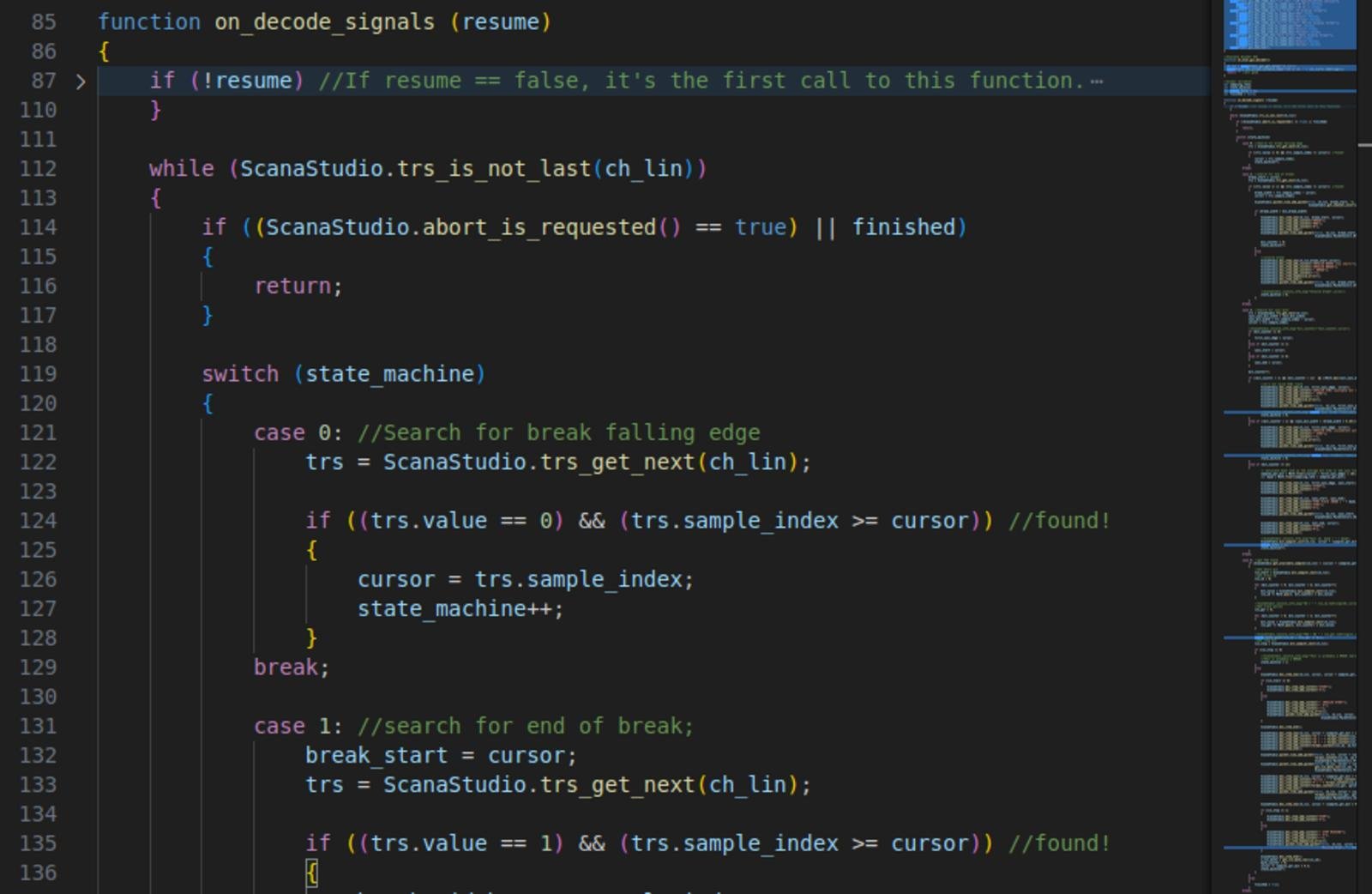

Decode or generate any protocol—or even your own proprietary logic patterns—with powerful scripting capabilities.

The SP1000G series supports fully scriptable decoders and generators through ScanaStudio’s JavaScript engine. Create or customize protocol analyzers, simulate device responses, or generate complex digital sequences tailored to your exact needs. Whether you’re working with industry standards or obscure, application-specific buses, SP1000G gives you full control over both capture and generation.

Learn more about Scripting

SP1000G Family

All SP1000G series devices share the same performance.

The only difference is the number of channels and internal memory size.

SP1018G

- 18 logic IN/OUT channels

- 1GSPS sampling & generation

- 4 GB internal memory

- USB 3.0 interface

SP1036G

- 36 logic IN/OUT channels

- 1GSPS sampling & generation

- 8 GB internal memory

- USB 3.0 interface

SP1054G

- 54 logic IN/OUT channels

- 1GSPS sampling & generation

- 12 GB internal memory

- USB 3.0 interface

Applications

- Validate parallel memory interfaces (SRAM, Flash, etc.)

- Inject custom test vectors into digital designs during silicon bring-up

- Emulate peripheral protocols (SPI, I2C, UART, etc.) in semiconductor validation setups

- Validate Design-for-Test (DFT) logic with scriptable, repeatable pattern sequences

- Capture and analyze responses from DUTs (Devices Under Test) with 1 ns resolution

- Trigger precisely on edge cases or functional events to debug critical timing paths

- Generate complex patterns for stress testing embedded systems and IP blocks

Benefits

- Accelerate semiconductor validation with programmable signal generation and capture

- Verify DFT logic early, reducing risk and cost at tape-out

- Replace bulky pattern generators with a compact, scriptable solution

- Automate your test bench with API-controlled generation and real-time response capture

- Maintain high fidelity even on large buses thanks to 1GSPS on up to 54 channels

- Stay flexible across projects with support for proprietary protocols and logic patterns

Frequently Asked Question

Can SP1000G generate and capture signals at the same time?

Yes. Absolutely! The SP1000G series features independent engines for signal capture and pattern generation, allowing simultaneous operation. You can inject test signals into your DUT while capturing its response on different channels—all with nanosecond-level precision. This full-duplex capability is ideal for debugging real-time interactions and validating protocol behavior.

How do I create custom test patterns for signal generation?

Custom patterns can be created using JavaScript-based scripting. You can define precise sequences, loops, delays, conditional branches and even pauses, waiting for operator interaction. For advanced use cases, pattern files can be loaded from external scripts or generated dynamically via the SP1000G API.

Can I use SP1000G to simulate I2C or SPI devices?

The SP1000G can reliably generate I2C, SPI, UART, and other protocol waveforms with precise timing and fully scripted sequences—making it ideal for simulating master devices or test pattern injection.

However, SP1000G does not respond in real time to input signals, so it cannot act as a true slave device that reacts dynamically to external masters. If your test scenario requires live interaction (e.g., simulating an I2C peripheral), a co-simulation with a microcontroller or FPGA may be required.

For generating complete communication scenarios—such as master write/read bursts, initialization sequences, or protocol stress tests—SP1000G remains a powerful and flexible tool in your validation workflow.

Is the SP1000G suitable for validating ASICs and FPGA designs?

Yes—SP1000G is particularly well-suited for semiconductor validation, including ASIC and FPGA testing. Its scriptable generation engine can inject test vectors into your digital design, while its 1GSPS capture engine monitors timing behavior and functional responses. Whether you're working on DFT validation, logic bring-up, or protocol emulation, SP1000G adapts seamlessly to your workflow.

What makes SP1000G better than a traditional logic analyzer?

Traditional logic analyzers capture signals. The SP1000G does both: capture and generate, in parallel. It acts as a logic analyzer, pattern generator, and test automation tool—all in one compact device. With 1GSPS sampling, up to 54 channels and advanced scripting, it brings high-end test capabilities to your bench without the bulk or cost of ATE systems.